사용자가 특정 차트를 고르면, 전 종목의 과거(10년) 차트들을 모두 탐색하여 가장 유사한 차트 10개를 골라 사용자에게 보여줍니다.

비슷한 차트 검색기

전 종목의 최근 10년간 모든 차트를 탐색합니다. 내 종목의 차트는 과연 상승하는 차트일까요?

www.similarchart.com

디지털시스템설계 수업을 듣고 인상 깊었던 점들이나 저에게 필요하다 싶은 내용들을 몇 가지 정리했습니다.

1. Boolean Algebra(불리언 대수)

불리언 대수 공식은 수학공식과 유사한 부분이 많지만, 제가 많이 햇갈려했던 공식을 적겠습니다.

(AB)' = A' + B'

(A + B)' = A'B'

AB + A = A

AB + A' = B + A' < 이게 제일 헷갈렸습니다.

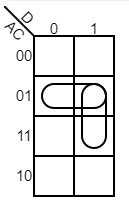

또한 회로를 표현하는 방법에는 Truth Table과 K-map(카르노맵)이 있습니다. Truth Table은 모든 경우의 수를 나열하는 표이고, K-map은 복잡한 논리식을 좀 더 편리하게 간소화시킬 수 있는 방법 중 하나입니다. 아래는 K-map입니다.

먼저, Truth Table로 참인 경우를 찾고, 표 안에 표시합니다.

인접해 있는 표시를 묶습니다. 0과 1이 상관없다는 뜻입니다. A'CD + A'CD' + ACD를 위와 같이 묶어 A'C + CD로 만들 수 있습니다.

2. 컴퓨터는 정보를 도대체 어떻게 저장할 수 있을까

항상 궁금했던 질문이었는데, 수업을 마친 지금은 이해하게 되어 시원합니다.

래치

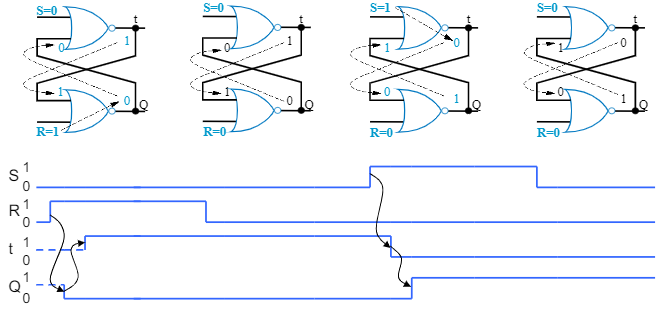

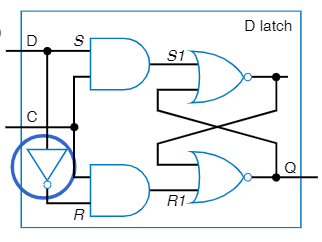

래치는 한 비트의 정보를 저장하는 회로입니다.

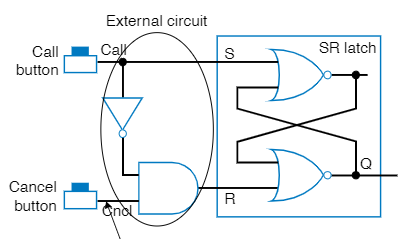

SR래치는 set이면 출력이 1, reset이면 출력이 0이지만, SR이 동시에 1이면 oscillate(진동)하는 문제점이 있습니다.

그렇다고 위 그림처럼 사이에 not을 넣으면 gate delay가 달라 glitch(원하지 않는 노이즈 펄스) 문제가 발생할 수 있습니다.

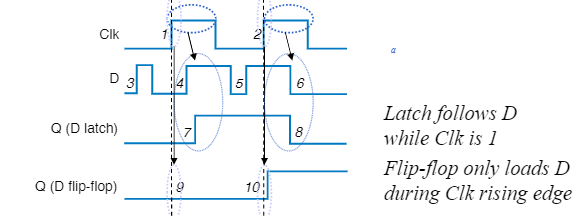

위와 같이 Level-Sensitive D Latch를 만들면 입력이 동시에 들어가 delay를 없앨 수 있습니다. 하지만, D latch를 연속적으로 붙이고 클럭(C)을 공유하면 얼마나 많은 래치가 바뀔지 모릅니다. 그래서 마지막으로 탄생한 것이

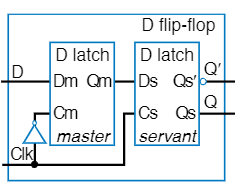

D 플립플롭

D filp-flop입니다. D래치 2개를 이어 붙이고, 한 클럭에 not을 붙이면,

위와 같이 clk이 올라갈 때만 출력이 나옵니다. 이렇게 딱 한 주기에 한 번만 정보가 저장됩니다.

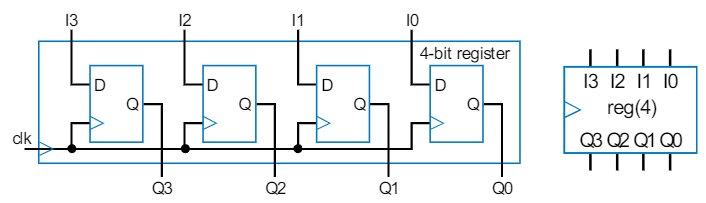

레지스터

이 플립플롭들을 여러 개 모아 클럭을 공유하면, 드디어 우리에게 익숙한 여러 비트의 정보를 저장하는 레지스터가 하나 완성됩니다!

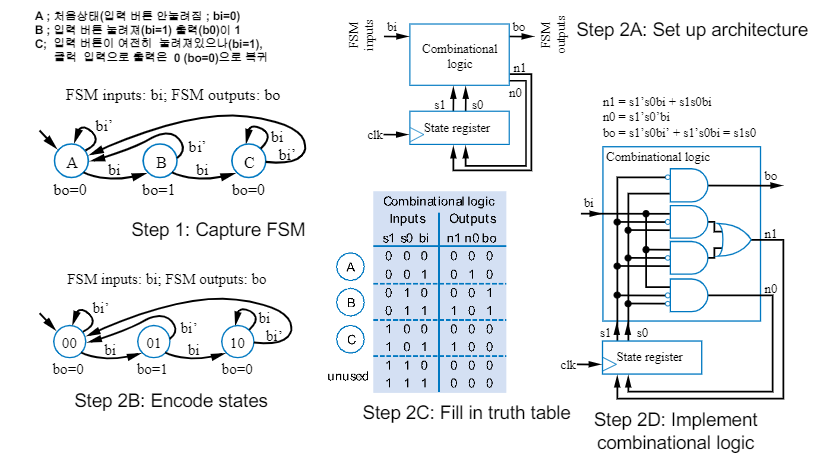

이제 controller design을 통해 원하는 회로를 설계하고, 직접 만들고 싶은 장치들을 만들 수 있습니다.

디시털시스템설계 느낀 점

저는 사실 하드웨어를 그리 좋아하지 않았습니다. 물리를 못하는 저에겐 너무 어렵게 다가왔습니다. 하지만, 역시 한번 해보는 것이 중요한 것 같습니다.

이전부터 이 컴퓨터는 도대체 어떻게 구성되어 있길래 정보를 저장할 수 있을까 궁금했습니다. 사실 이전에도 컴퓨터 구조 책에서 래치와 플립플롭에 관련된 내용을 접한 적이 있습니다. 그때는 이해하기 매우 힘들어 '아 나는 역시 회로랑은 안 맞아'라고 단정 지어 버렸습니다.

하지만, 기본 and or게이트부터 시작하여 차근차근 레지스터까지 문제점을 해결하며 발전해 온 것을 따라오다 보니, 이해하기 쉬웠습니다.

이제 궁금증을 해결함과 동시에 세상을 보는 눈이 달라졌습니다. 어떤 전자장치를 보면, 아 이 장치는 회로가 이렇게 구성돼있겠구나, 생각보다 만들기 쉽겠는데? 하는 생각이 들었습니다.

처음에는 전공필수과목이라 어쩔 수 없이 듣는 거지 전공선택이었으면 듣지 않았을 것이다라고 생각했지만, 컴퓨터를 좋아하는 사람이라면 이 내용을 알 필요가 있다고 생각합니다.

'대학수업정리' 카테고리의 다른 글

| 규칙 기반 챗봇 만들기 프로젝트(22.12.24) (0) | 2024.02.14 |

|---|---|

| 시스템 프로그래밍 정리(22.12.22) (0) | 2024.02.14 |

| 2-2 인공지능개론 정리(22.12.19) (0) | 2024.02.14 |